My Stops |

|

present

Lecturer at the University of Manchester in the Advanced Processors Technologies group.

I work on methodologies, tools and applications for accelerating compute intensive tasks in embedded systems and high-performance computing systems using non-conventional approaches.

This includes in particular reconfigurable technology (such as FPGAs) for building custom computing pipelines.

|

|

2013

Postdoc at the University of British Columbia Vancouver (CA).

I was invited by Prof. Guy Lemieux for giving his lecture Parallel and Reconfigurable Computing and for exchanging ideas.

We worked on FPGA virtualization techniques and computer architecture related topics. One result was a paper "An Efficient FPGA Overlay for Portable Custom Instruction Set Extensions" at FPL.

Guy has founded VectorBlox which is a start-up selling a vector processor overlay for FPGAs that gives quite some impressive performance gains over traditional softcore processors.

|

|

2009-2013

Postdoc at the University of Oslo (Norway) in the Robotics and Intelligent Systems (ROBIN) group.

As a postdoc, I led the COSRECOS project which aims at making partial reconfiguration more accessible on FPGAs. In 2012, I was program co-chair and co-organizer of the FPL 2012 conference in Oslo.

|

|

2003-2009

Research assistant at the University of Erlangen-Nuremberg (Germany) in the Hardware-Software-Co-Design group (chaired by Prof. Jürgen Teich).

During my PhD time, I worked on distributed embedded reconfigurable FPGAs-based systems and applications.

|

|

until 2003

Student at the University of Paderborn (Germany).

I studied electrical engineering with emphasis on power electronics and analog circuit design.

My diploma project (done at the QUT Brisbane , Australia) was on mapping a neural network on the coarse grained PACT XPP architecture.

|

My Projects |

|

ECOSCALE - Energy-Efficient Heterogeneous Computing at Exascale

ECOSCALE refines HPC systems to tackle scalability and energy efficiency challenges that will arise at exascale performance. This will be done by employing a scalable programming environment and hardware architecture tailored to the characteristics and trends of current and future HPC applications, reducing significantly the data traffic as well as the energy consumption and delays.

ECOSCALE Project Website

This project is supported by the European Commission under the Horizon 2020 Program H2020-ICT-671632.

|

|

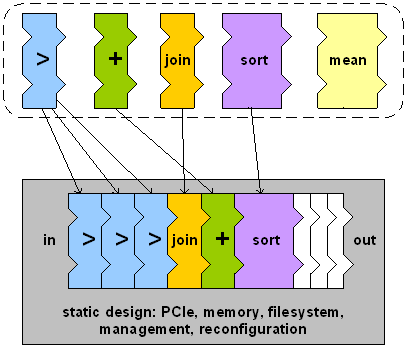

Database Acceleration with FPGAs

Currently, I work with two students (Ziyad Gideir and Petrut Bogdan) on query acceleration for databases using a MAX3 FPGA stream processing machine from Maxeler Technologies.

This extends the work I started together with my master student Jonas in Oslo (get his master thesis here).

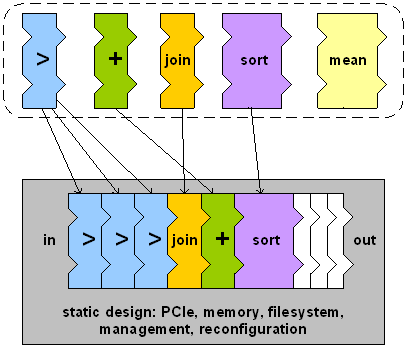

The idea is to stitch a pipeline of pre-built (SQL)-operator modules together on-the-fly in order to accelerate the currently requested query.

With a capacity of more than 1000 32-bit instructions on the given FPGA, we expect a computational throughput of up to 20 GB/s.

|

|

GoAhead - Second Generation FPGA PR Tools

GoAhead is our second generation tool for building partially reconfigurable systems using Xilinx FPGAs.

GoAhead is the by far most advanced PR tool by today. It provides a comfortable GUI, but it can also be fully script controlled.

Moreover, we provide unique features no other tools have addressed including design-rule checks, timing verification and automatic floorplanning.

GoAhead enabled systems support module relocation in a very fine tile grid, multi-module instantiation, crossing of static signals through reconfigurable regions,

hierarchical reconfiguration (a PR module inside a PR module) and very flexible communication mechanisms.

This work is carried out with my PhD student Christian Beckhoff who will graduate this year.

|

|

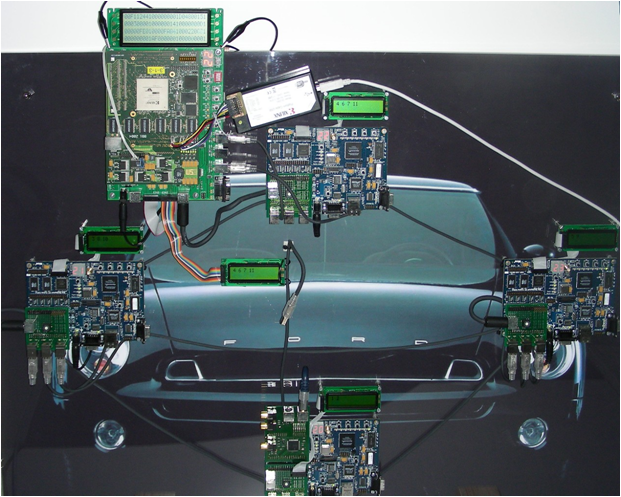

Reconfigurable Networks - ReCoNets

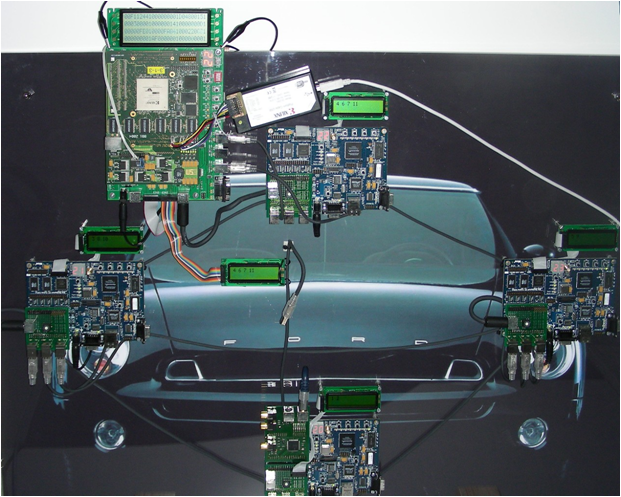

One of my PhD projects was about building a design methodology for embedded systems made upon small networks of hardware reconfigurable nodes and connections.

In our ReCoNets demonstrator, broken links can be repaired by rerouting.

Similarly, broken nodes can be masked by activating (redundant) replica tasks on the remaining nodes.

This is possible without losing internal states for both software tasks and hardware tasks (running on an FPGA in each node).

It is even possible for some tasks to change the execution style between software and hardware dynamically at run-time

(something we called Hardware/Software Morphing - search for "Modeling and Synthesis of Hardware-Software Morphing" in the ReCoNets publications page)

|

|

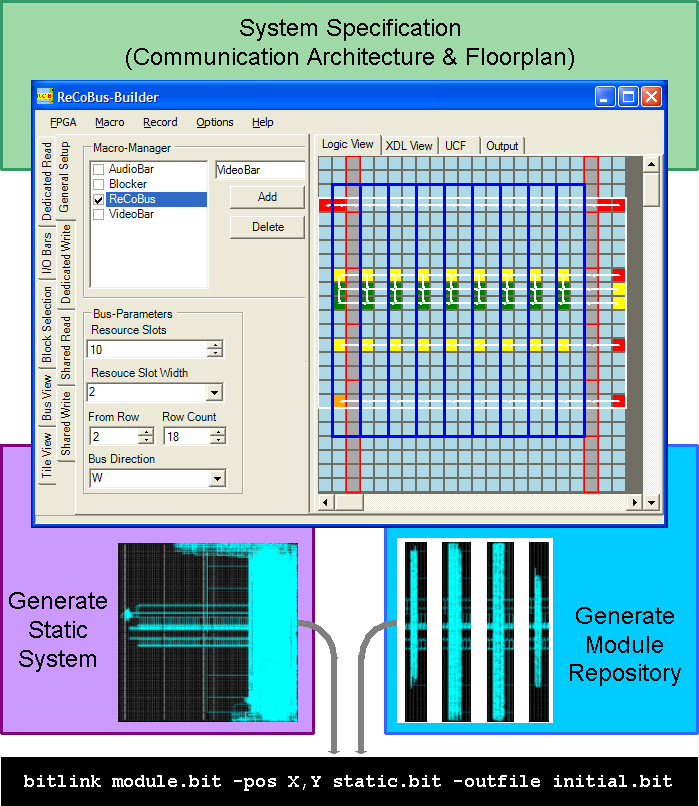

ReCoBus-Builder - Advanced FPGA PR Tools

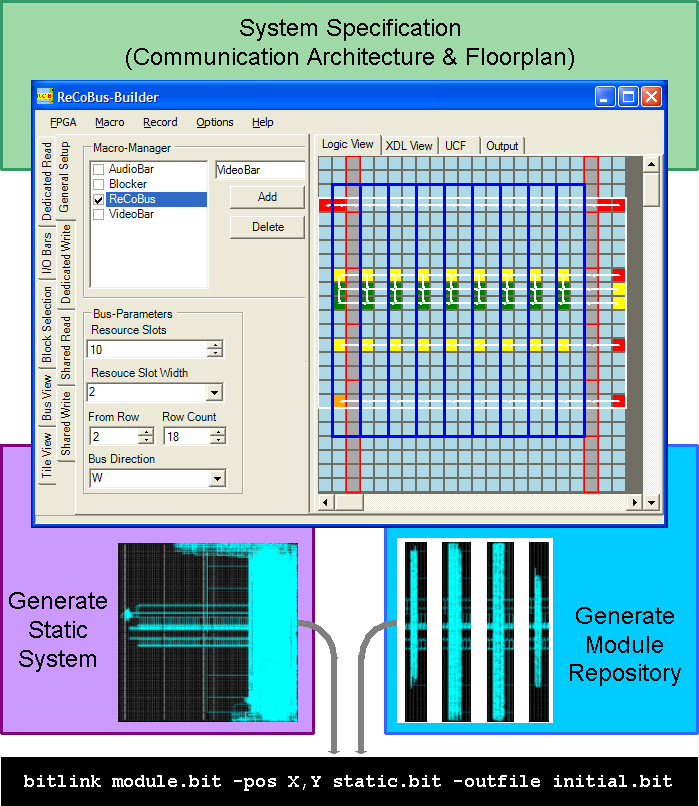

ReCoBus-Builder is our first generation tool set for building partially reconfigurable systems using Xilinx FPGAs (for all Spartan-3 and Virtex-II/-Pro devices).

Our ReCoBus-Builder paper which was published at the FPL'08 and has been cited more than 80 times.

The ReCoBus-Builder was used to implement the ReCoNets demonstrator.

With this tool, we built a test system with more than a hundred parallel executed modules that could each be individually accesses via a ReCoBus and that could all manipulate a video stream.

See also our paper "A Bus-based SoC Architecture for Flexible Module Placement on Reconfigurable FPGAs" for a nice ReCoBus demonstration.

|

|

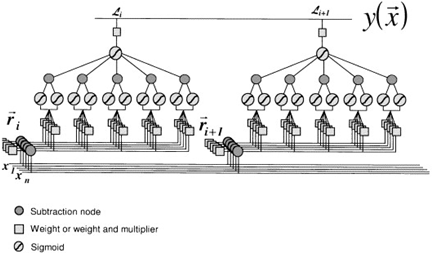

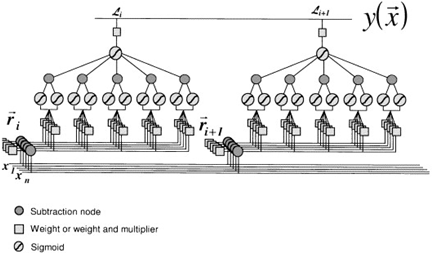

Neural Function Approximation

I implemented a Local Cluster Neural Network (LCNN) on the PACT XPP architecture as part of my master project.

LCNNs have similarities to radial basis function networks, but have much better modeling capabilities.

One outcome of this project was that digital processing can be more beneficial with respect to power, area and performance than analog processing.

LCNNs are also suited for hardware-supported learning.

This is a video on training an LCNN .

|

|

6502 Mini Computer

During high school time, I built a small 6502 computer.

I programmed this machine using assembly language with my Commodore 64.

I also built an EPROM programmer that used some of the C64 PIO pins from the keyboard to drive the EPROM address lines.

Another interesting thing is that the keyboard of my computer needed only one I/O pin.

I encoded the rows with different frequencies and the columns with different pulse lengths.

All these projects made lots of fun!

|

My Books |

|

FPGAs for Software Programmers

This book introduces FPGA technology to software developers by giving an overview of FPGA programming models and design tools, as well as various application examples.

The book covers in particular a wide range of high-level programming approaches and is also of interest for hardware designers who want to develop hardware accelerators at higher abstraction levels and with better design productivity. I am co-editor and a chapter co-author of this book.

Get it here

(see the book flyer here).

|

|

Partial Reconfiguration on FPGAs - Architectures, Tools and Applications

This book is a "must read" for everybody who is interested in partial reconfiguration on FPGAs. It covers theoretical background, techniques and limitations, but also applications that benefit from partial reconfiguration.

Get it here

(or here, if you have a Springer online subscription).

|

|

Dynamically Reconfigurable Systems - Architectures, Design Methods and Applications

This book is an outcome of the Priority Program on ”Reconfigurable Computing Systems” funded by the German Research Foundation (DFG).

I contributed to two chapters in this book.

Get it here.

|

|

Proceedings of the 22nd Conference on Field Programmable Logic and Applications (FPL)

I was co-editor of the FPL2012 proceedings.

FPL is the oldest and biggest annual conference which is dedicated to FPGA technology.

For its 22nd edition, we compiled a program with 50 papers and 60 poster presentations.

Moreover, we had over 300 international attendees in Oslo (one third more than the year before).

Get the proceedings here.

|

My Courses |

| present |

Mobile Systems (lectures), The University of Manchester.

|

| 2013 |

EECE 528 Parallel and Reconfigurable Computing (lectures & labs), University of British Columbia, Vancouver, CA

|

| 2011 – 2013 |

INF 5430 Advanced Digital Systems Design (lectures & labs), University of Oslo, Norway |

| 2003 – 2008 |

Fundamentals in Computer Engineering (lectures (per procurationem), tutorials, labs), University of Erlangen-Nuremberg, Germany |

| 2004 – 2005 |

Embedded Systems (tutorials and labs), University of Erlangen-Nuremberg, Germany

|

| 2006 |

Parallel Systems (labs), University of Erlangen-Nuremberg, Germany

|

| 2007 – 2008 |

Reconfigurable Computing (labs), University of Erlangen-Nuremberg, Germany

|